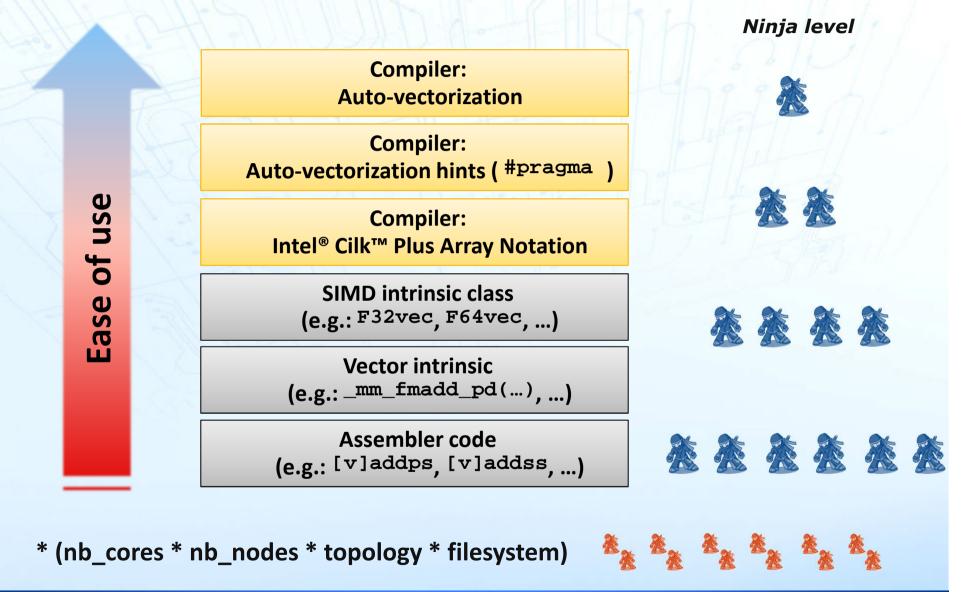

# Will the future computers be restricted to Ninja programmers?

Philippe Thierry Energy Engineering Team Intel Corp.

#### 1. Who and Where are the Ninjas?

2. What is the « computer of the future »?

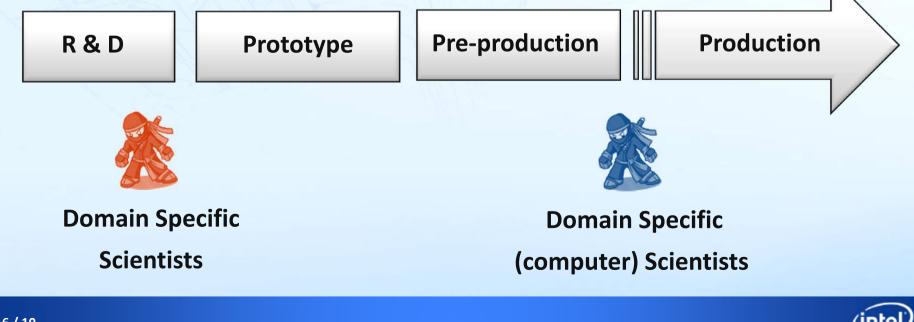

## The Who

- Computer Scientists:

- We know what we are doing. Get out of our way.

- We are Ninjas. And we want to publish.

- Scientists:

- Research grants and publishing are our life-blood.

- We'll do Ninja programming if it gives interesting publishable results.

- Industry- End Users / ISV :

- Our business is not the computer science.

- We have Ninja's, but we want them spending time on the science.

- We will invest in Ninja work only if the ROI is high enough.

- Standards and modular models are great.

- Differentiation vs our competition is great.

# The Where

## **Org Chart : How to succeed**

**Cross Domain Specialists**

#### Forward Looking Team – Hdw / Sftw

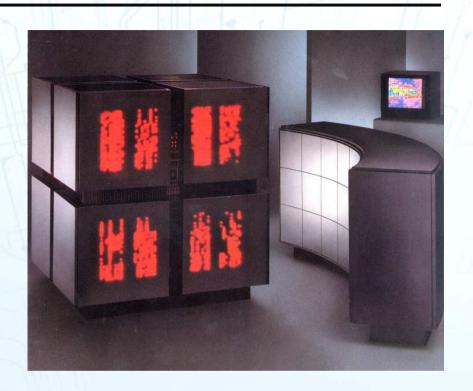

#### **Computer of the future : Like this one ?**

### just kidding , this one is from 1987

A "massively parallel" hypercubic arrangement of **32k single bit processors**

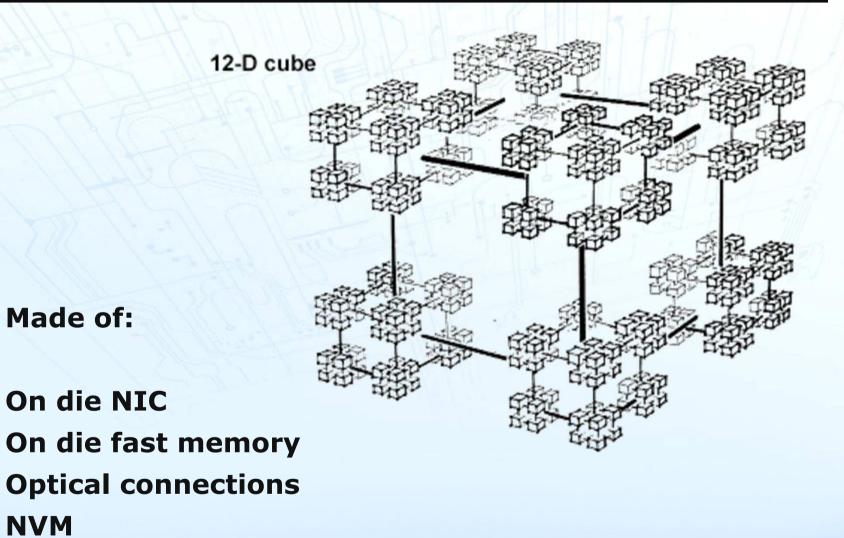

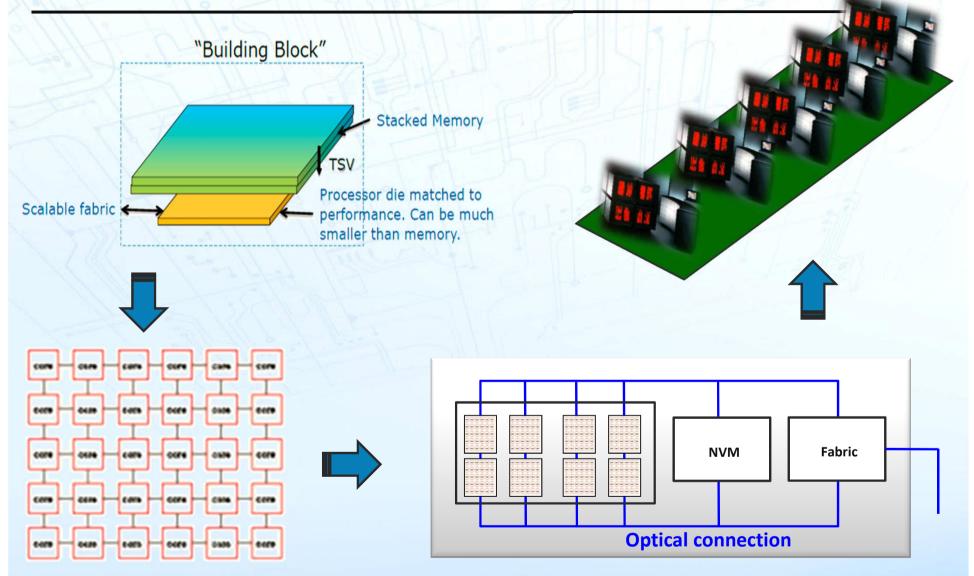

### **Computer of the future : Like this one ?**

#### Summary

- Machine: Power remains the major issue but new technologies are coming

- = f( bandwidth / Latency / power / capacity / locality / flops / price)

- Huge data arrives too .

- Prog Model:

- Standards will stay for years and Fortran remains a FORmula TRANslator

- Keep eyes on new things for 5% of eXtreme applications

- Algo: Perf. gains will come from parallelism (data and thread)

- Data movements (even on-chip) will become more and more expensive

- Data locality and Topology are keys

- Move the code not the data

- Manage heterogeneities (cores, memory hierarchies)

#### Summary

#### Then, YES,

- Future computers will be for Ninja <u>as for today (meaning not only)</u>

- Optimization space is getting larger

- Gang of Ninja will have more chance to succeed

- If they have and share the right tools

- Need to start training now with current multi and many-cores

- If not already late

#### **Optimization Notice**

Intel<sup>®</sup> compilers, associated libraries and associated development tools may include or utilize options that optimize for instruction sets that are available in both Intel<sup>®</sup> and non-Intel microprocessors (for example SIMD instruction sets), but do not optimize equally for non-Intel microprocessors. In addition, certain compiler options for Intel compilers, including some that are not specific to Intel micro-architecture, are reserved for Intel microprocessors. For a detailed description of Intel compiler options, including the instruction sets and specific microprocessors they implicate, please refer to the "Intel<sup>®</sup> Compiler User and Reference Guides" under "Compiler Options." Many library routines that are part of Intel<sup>®</sup> compiler products are more highly optimized for Intel microprocessors than for other microprocessors. While the compilers and libraries in Intel<sup>®</sup> compiler products offer optimizations for both Intel and Intel-compatible microprocessors, depending on the options you select, your code and other factors, you likely will get extra performance on Intel microprocessors.

Intel<sup>®</sup> compilers, associated libraries and associated development tools may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include Intel<sup>®</sup> Streaming SIMD Extensions 2 (Intel<sup>®</sup> SSE2), Intel<sup>®</sup> Streaming SIMD Extensions 3 (Intel<sup>®</sup> SSE3), and Supplemental Streaming SIMD Extensions 3 (Intel<sup>®</sup> SSSE3) instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors.

While Intel believes our compilers and libraries are excellent choices to assist in obtaining the best performance on Intel<sup>®</sup> and non-Intel microprocessors, Intel recommends that you evaluate other compilers and libraries to determine which best meet your requirements. We hope to win your business by striving to offer the best performance of any compiler or library; please let us know if you find we do not. Notice revision #20101101

#### Legal Disclamer

INFORMATION IN THIS DOCUMENT IS PROVIDED "AS IS". NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO THIS INFORMATION INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

Performance tests and ratings are measured using specific computer systems and/or components and reflect the approximate performance of Intel products as measured by those tests. Any difference in system hardware or software design or configuration may affect actual performance. Buyers should consult other sources of information to evaluate the performance of systems or components they are considering purchasing. For more information on performance tests and on the performance of Intel products, reference <u>www.intel.com/software/products</u>.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2010. Intel Corporation.